Electronique numérique & FPGA

Progressivement envahit par le numérique, je me décide donc à apporter ma pierre à

l'édifice de la culture concernant ce domaine. Et comme je suis le genre

de personne qui aime bien faire profiter aux autres de son ignorance, (comme dirait Gotlib),

je vais vous expliquer cela dans les moindres détails.

Plus sérieusement, après ce préambule de haut niveau rédactionnel, ce document est basé

sur la compréhension du développement fpga Xilinx. Il s'agit d'une brève introduction, ou

tutorial, permettant d'appréhender le concept général qui est valable quelque soit le

circuit dans lequel sera implémenté la logique. (c'est le logiciel qui s'occupe de tout

à ce niveau là, les fabricants proposant des logiciels spécifiques à leurs cibles.)

Si le coeur vous en dit, il est possible après d'analyser la faisabilité d'un décodeur

nagravision. (principe de la corrélation numérique entre lignes successives.)

Citons quelques fabricants de FPGA parmi les plus connus :

Le site de XILINX

Le concurrent principal Altéra

Actel

AMD

Cypress

Ne pas omettre de faire un tour sur le forum vhdl:

forum international vhdl

Pour finir cette entrée en matière, deux logiciel de simulation vhdl dos ou linux, avec ou sans licence:

Symphonie

Model Sim

La partie suivante présentera la famille des FPGA xilinx, les possibilités, comment les

utiliser, ou trouver des cartes d'évaluation...

La seconde partie traitera de la conception numérique schématique, suite à quoi, nous

passerons à une modélisation syntaxique VHDL, sans doute, la plus largement répandue,

du moins en Europe, les américains préférant le Verilog.

Il est grandement conseillé de comprendre ce qui se cache derrière les lignes de code vhdl,

sans quoi, la transcription du code vhdl lors de l'implémentation risque fort de donner

quelque chose de lourd, voir même faux.

Introduction & présentation des FPGA xilinx.

Petit lexique en introduction :

SLICE : cellule élémentaire du fpga ; composé de 2 LUTs et 2 bascules.

BANK : zone d'interconnection périphérique du fpga.

CLB : Configurable logic block : bloque logique configurable : comprend 4 slices similaires.

IOB : Input Output Block : broches d'entrées sorties.

La structure de base des FPGA des différentes familles Xilinx est généralement la même, à savoir constituée :

- de CLB : blocs logiques programmables (configurable),

- d'IOB : blocs logiques d'entrées/sorties.

- Mémoires RAM de 4096 bits,

- Horloges DLL pour le réseau de distribution...

Deux générateurs de fonction à 4 entrées (LUT : Look Up Table) sont disponibles dans chaque CLB permettant

la réalisation de toutes fonctions booléennes des 4 entrées.

En fait, ces LUT sont des cellules de RAM de 16 fois 1 bit, ou peuvent être considérée comme tel, réalisant la table

de vérité de la fonction logique souhaitée. Ces LUT peuvent être utilisées comme SRL, registre à décalage 16 bit

programmable.

Les CLB disposent par ailleurs de chaînes de Carry (retenue) et bien sur, de bascules (2bascules et 2LUTs par slice).

Les IOB, quant à eux, sont positionnés à la périphérie du circuit et peuvent supporter différents standards (LVCMOS,

LVDS, LVTTL...) Des bascules sont intégrées aux IOB afin de pouvoir synchroniser le signal aux entrées et sorties du Xilinx.

Chaque IOB peut-être configuré en entrée ou sortie, avec buffer trois-états ou buffer de niveau classique selon le standard.

Ces entrées/sorties sont organisées par bank aux alimentations spécifique (attention à être compatible avec le standard) ;

ces IOB sont par ailleurs appairés : généralement N et P (pour les signaux différentiels).

On se reportera aux datasheet des différentes références pour plus de détails.

Ci-dessous le représentation d'un demi slice, on peut voir la présence d'une LUT et d'une bascule ainsi sue divers

éléments présents dans chaque sclice : carry chaîne, multiplexeur..

C'est le temps de propagation des signaux qui constitue la limite de fonctionnement du circuit. Ce temps de routage

entre deux blocs dépend en premier lieu de la technologie de gravure utilisée. Puis, du taux de remplissage du composant

ainsi que du moteur d'implémentation-routage. D'une façon générale, on spécifie les contraintes de temps dans un fichier,

le logiciel de routage s'arrange pour les respecter.

Dans certains cas extrêmes, il est nécessaire d'imposer la position des éléments (bascule ou LUT), sachant que les slice en

diagonales ont le temps de routage le plus faible.

Là aussi, on se référera à la datasheet pour plus de détail. Précisons simplement que le Xilinx est constitué par quatre

quadrants, chacun peut disposer seulement d'un nombre restreint d'horloge différentes...

Les DLL, sont des composants d'horloge dont on peut définir la phase du signal à sa sortie; elles peuvent par ailleurs

générer des signaux de fréquence multiple selon certains rapport (double, 1,5x ...)

Méthodologie de développement.

Le code source écrit en vhdl, pourra être simulé à l'aide de l'outil symphony, relativement puissant et convivial, la

version de base suffit largement pour l'utilisateur lambda. Une société aura tout intérêt à acheter la licence.

Les fichiers vhdl correctement simulés, on précise dans un fichier de contraintes à l'extension 'ucf' les différents

paramètres utiles, au moins le brochage et sans nul doute quelques contraintes de temps, éventuellement de placement.

L'outil xilinx project navigator permet la synthèse du code vhdl (avec XST) et son implémentation (PAR). XST génère une

netlist au format edif (ou similaire ngo) qui n'est autre que la structure au niveau composants (vue RTL).Cette netlist

ainsi que le fichier de contrainte sert de base à l'outil de placement & routage (PAR).

Les différentes familles Xilinx, liste non exhaustive, se référer au site web xilinx :

| Famille | Référence | LUTs | Bascules | Slice | Cellules logiques | ordre de prix |

| VIRTEX II | XC2V40 | 512 | 512 | 256 | 576 | 39$-CS144-5-(1) |

| VIRTEX II | XC2V80 | 1024 | 1024 | 512 | 1152 | 70$-CS144-? |

| VIRTEX II | XC2V250 | 3072 | 3072 | 1536 | 3456 | BGA |

| VIRTEX II | XC2V500 | 6144 | 6144 | 3072 | 6912 | BGA |

| VIRTEX II | XC2V1000 | 10240 | 10240 | 5120 | 11520 | BGA |

| VIRTEX II | XC2V1500 | 15360 | 15360 | 7680 | 17280 | BGA |

| VIRTEX II PRO | XC2VP2 | 2816 | 2816 | 1408 | 3168 | ?? |

| VIRTEX II PRO | XC2VP4 | 6016 | 6016 | 3008 | 6768 | ?? |

| SPARTAN II | XC2S50 | 1536 | 1536 | 768 | 1728 | 16$-TQ144-6-(1) |

| SPARTAN II | XC2S100 | 2400 | 2400 | 1200 | 2700 | 19$-TQ144-5-(1) |

| SPARTAN II | XC2S150 | 3456 | 3456 | 1728 | 3888 | 14$-PQ208-5-(24) |

| SPARTAN II | XC2S200 | 4704 | 4704 | 2352 | 5292 | 28$-PQ208-5-(nd) |

| SPARTAN II | XC2S300 | 6144 | 6144 | 3072 | 6912 | 60 Euros |

| SPARTAN IIE | XC2S50E | 1536 | 1536 | 768 | 1728 | ?? |

| SPARTAN IIE | XC2S100E | 2400 | 2400 | 1200 | 2700 | 21$-PQ208-6-(24) |

| SPARTAN IIE | XC2S200E | 4704 | 4704 | 2352 | 5292 | 27$-PQ208-6-(24) |

| SPARTAN IIE | XC2S300E | 6144 | 6144 | 3072 | 6912 | ?? |

| SPARTAN IIE | XC2S400E | 9600 | 9600 | 4800 | 10800 | ?? |

| SPARTAN IIE | XC2S600E | 13824 | 13824 | 6912 | 15552 | ?? |

Quelques remarques concernant le tableau :

Les SPARTAN II et SPARTAN IIE possèdent sensiblement les mêmes caractéristiques ; la version SPARTAN II est réalisée en

technologie 0.22 ou 0.18um, alimentation en 2.5Volts, ce qui permet, entre autre, des fréquences maximales des DLL de

200MHz.

Les version SPARTAN IIE sont quant à elles en technologie 0.18um ou 0.15um, alimentation 1.8Volts permettant des

fréquences de 320MHz.

TQ, HQ, VQ, PC sont des boîtiers dont les E/S sont à la périphérie, CS, BG ect sont ds boitiers type BGA ; on en conclut

que les virtex II et virtex II pro ne peuvent pas être utilisés facilement par l'amateur (particulier).

Les différentes cartes d'évaluations :

Plusieurs fournisseurs proposent des cartes d'évaluation pour composants programmables.

Insight

Carte basée sur port USB

Xess

AVNET (pour les sociétés seulement)

Xess :

XSA-50 à base du SPARTAN II XC2S50, 8Mo de SDRAM, 128ko de flash, afficheur 7 segments... 149$

XSA-100 à base du SPARTAN II XC2S100, intègre 16Mo de SDRAM, 256ko de mémoire flash, afficheur 7 ségments et oscillateurs...

Ils fournissent un logiciel qui programme la carte par le port parallèle. prix : 279$.

Proposent un CD-ROM logiciel, Model Sim (simulateur vhdl), Xilinx web_pack, datasheet...

X2s_usb :

A base du SPARTAN XC2S200, programmation par le port USB. 299 Euros.(windows seulement)

quelques autres carte d'évaluation dont une PCI.

Insight :

Evaluation kit : SPARTAN II LC, basé sur le XC2S100PQ208, 2afficheurs 7 segments, PROM. 155$

La même chose avec cable JTAG et CDrom Web pack pour 185$.

Evaluation kit : SPARTAN III version S50. 135$ ; 185$ avec cable JTAG et CDrom.

AVNET :

Xilinx SPARTAN II évaluation kit à base de XC2S150, intègre une prom série XC18V01, un thermomètre SPI, un port RS232...149$

Le câble JTAG vous en contera de 95 $.

Xilinx VIRTEX II évaluation kit à base de XC2V1000, boitier FG256 broches. 400$

Xilinx SPARTAN IIE évaluation kit, à base de XC2S200E

Les différents modes de fonctionnement des FPGA Xilinx :

Si l'utilisation de la carte d'évaluation permet de débugger un projet, généralement on souhaite intégrer le composant FPGA

dans une carte cible autonome. A prioris, deux possibilités, vous disposez d'un CPU puissant, avec mémoire non volatile et

bus, dans quel cas il est possible de programmer le Xilinx par ces éléments. Ou alors, il n'y a que le xilinx de numérique,

dans quel cas, il est maître et récupère le binaire d'une PROM externe. C'est cette dernière solution qui est retenue pour

le fréquencemètre.

Quelques soit la famille, différents modes de programmations existent selon le niveau logique des broches

M0/M1/M2. On se reportera à la datasheet pour les détails. La configuration en mode maître série est déterminé par les

trois broches de mode au niveau logique zéro.

Rien de bien original dans ce schéma, juste une PROM Xilinx qui contient le programme (le contenu binaire du FPGA).

Cette mémoire est à accès série dans mon cas, l'horloge est fournit par le FPGA cablé en mode maître. Cette horloge est

la seule entrée de la PROM qui intègre donc le compteur d'adresse.

Le schéma ci-dessous représente la façon d'interconnecté la PROM à plusieurs composants programmables. Le premier en maître

fournit l'horloge à la PROM, le second en esclave reçoit les données d'une sortie du composant maître.

Détail sur les différents mode de programmation du composant, JTAG...

Les domaines d'applications sont innombrables, on trouvera sur ces pages un fréquencemètre qui se prête

relativement bien à cette technologie.

Il est prévu aussi d'extaire une chaîne télé du train MPEG. Voir la partie récepteur TNT COFDM.

(montages électronique).

Description schématique & VHDL de fonctions numériques.

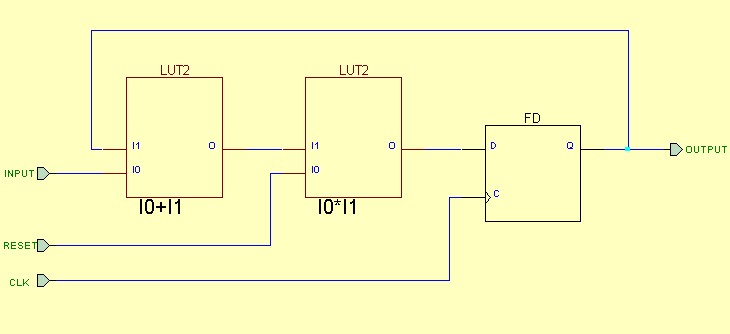

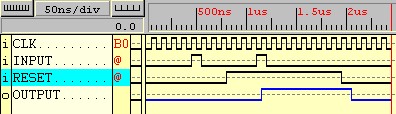

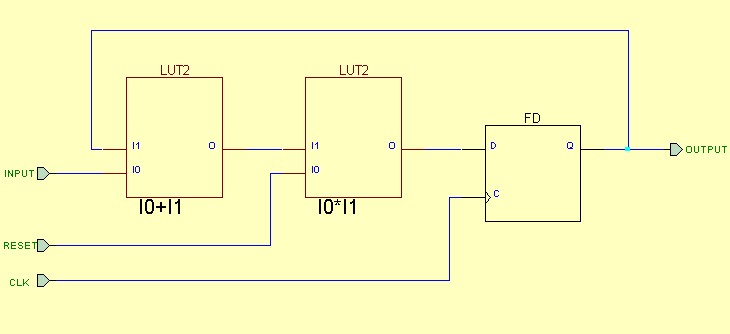

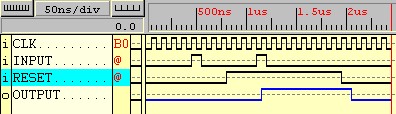

Mémorisation d'une information (pulse quelconque). Cela nécessite de mémoriser dans une bascule le "ou" logique

entre l'entrée et le signal de sortie de la bascule.

Une logique intermédiaire permet de mettre à zéro la sortie mémorisée(reset).

Donc, pour résumer, le signal reset consiste en un raz (remise à zéro) prioritaire, et input

réalise la mise à un.

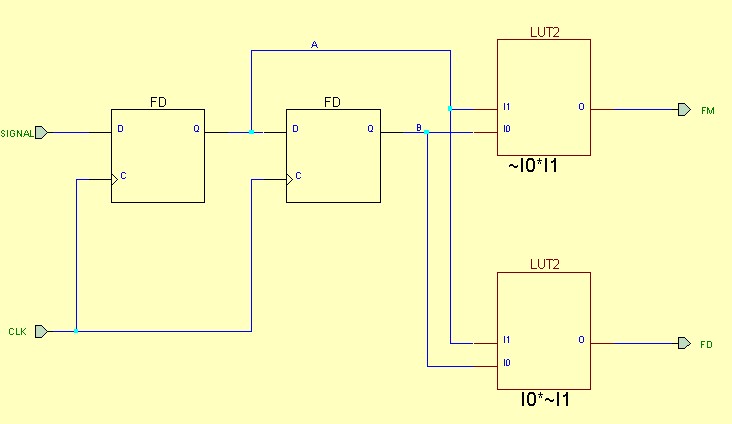

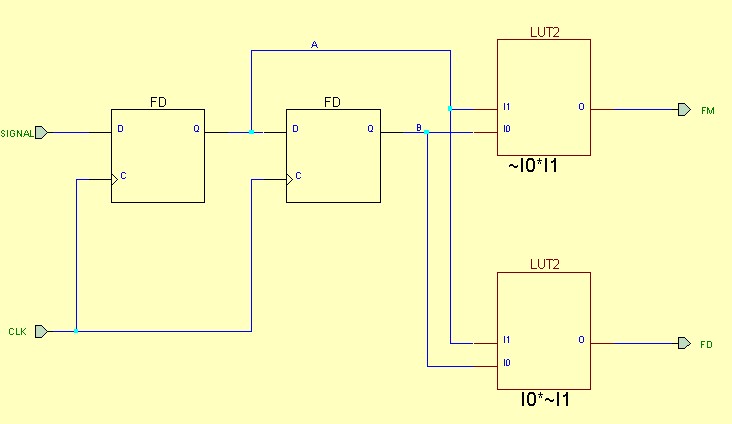

La détection de front montant ou descendant se fait en retardant le signal et en le comparant

avec celui d'origine (signaux A et B). La détection de front montant ou descendant est alors

facile à réaliser. Le signal sur lequel est effectue la détection de fronts s'appelle ici

"signal". (pourquoi pas!)

La présence de la première bascule permet