1. Principe de fonctionnement :

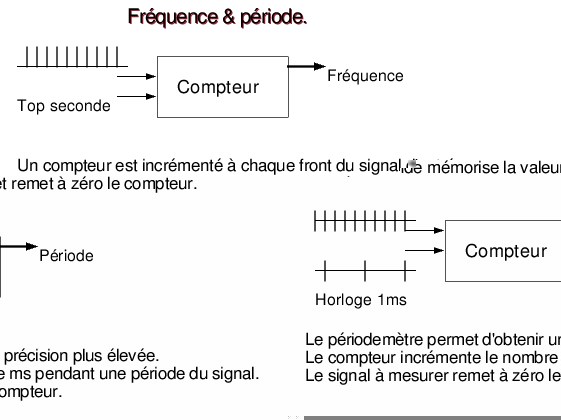

Le Hertz (Note 1) est définit comme étant le nombre de transition d'un signal dans une seconde.

Le principe de la mesure consiste donc à compter les impulsions du signal à mesurer pendant une

seconde. Le résultat du compteur est mémorisé et réactualisé à chaque seconde puis envoyé sur un

afficheur.

Pour mesurer des fréquences faibles, le mode périodemètre est généralement utilisé afin d'avoir

une meilleure précision sur le résultat. Dans ce cas, le signal à mesurer définit l'enveloppe

de comptage d'une horloge de référence de 1ms ou 1us. Le système compte donc le nombre de ms pendant

une période du signal. (Une détection de front montant du signal à mesuer permet de mémoriser

et remettre à zéro le compteur millisecondes, ce qui permet de s'affranchir du rapport cyclique.)

Mesure de fréquence et période.

Pour réaliser notre fréquencemètre, il est possible de faire appel aux timer internes d'un

micro-contrôleur, ou plus simplement utiliser une multitude de compteur diviseur par 10. La solution

retenue ici est l'utilisation d'un FPGA d'entrée de gamme.

Les circuits CMOS permettent des mesures jusqu'à 40 ou 50MHz au maximum; les circuits numériques

tels que les FPGA fonctionnent jusqu'à 100 ou 200MHz (400MHz pour les plus performents).

Il est donc nécessaire d'abaisser la fréquence incidente. Pour cela un prédiviseur est utilisé. Ici

le choix s'est porté sur un circuit admettant une fréquence maximum de 1 GHz et une division de 128,

mais rien n'empèche l'utilisation du MB506 par exemple qui accepte des fréquences de 2.5GHz et éffectue

une prédivision de 256.

La prédivision de 128 est relativement facile à traiter et ne consiste qu'à une succession de sept

décalages; une entrée matérielle permettra de sélectionner le facteur prédivision choisit.

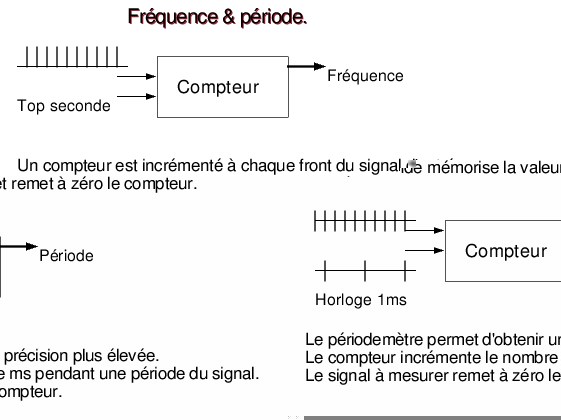

Synoptique du fréquencemètre.

Afin d'assurer une bonne sensibilité de mesure, un amplificateur est placé devant le pré diviseur, il

s'agit d'un hybride, ampli monolithic large bande style ERA5/INA10386... qui nécessite relativement peu de

composants externes. (capacité de découplage, polarisation)

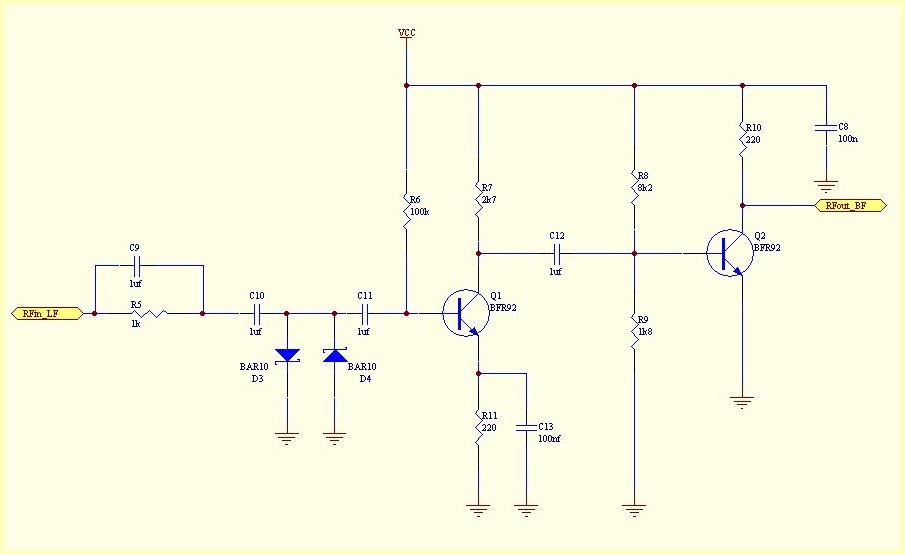

Une deuxième entrée (BF ou LF) est utilisée pour des fréquences inférieures à 200MHz, le prédiviseur ne

fonctionnerait plus très bien pour des fréquences faibles. Dans ce cas, le signal est aussi amplifié par

des étages à transistors cette fois.

Ces deux signaux sont envoyés vers deux entrées du composant programmable et attaqueront le compteur; la

commutation est faite au niveau du traitement numérique par un multiplexeur d'horloge. (voir ci-dessous).

La référence de temps de 10MHz permet de générer les différentes horloges de traitement : 1seconde, 1ms et 1us.

Cette référence doit évidemment avoir une bonne précision et une faible dérive afin d'assurer une bonne mesure.

Un quartz peut faire l'affaire mais dérivera en température, sinon le choix se portera sur l'utilisation d'un

VCXO ou d'un TCXO (oscillateur controllé en température). Tout dépend de la précision désirée (et du budget).

2. Analyse détaillée et schémas :

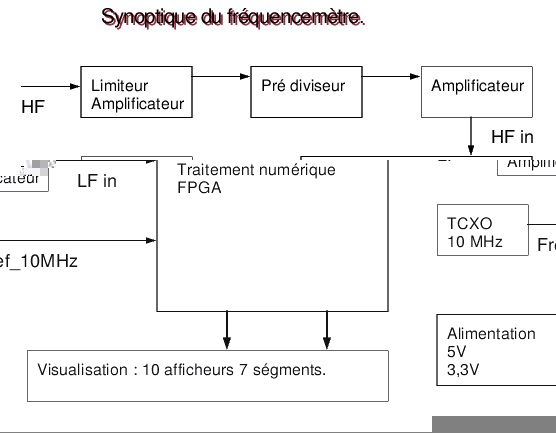

Schéma de la partie VHF.

Après ces premières considérations, voyons la partie matérielle du montage. Comme prévu, rien de bien compliqué, un oscillateur à 10MHz controlé en température (TCxO) attaque une entrée du FPGA, deux autres entrées, HF et BF sont issues du traitement analogique. Les diodes de limitation d'entrées servent à protéger le prédiviseur contre les tensions d'entrée excessives : les capacités de liaison permettent de couper la composante continue entre les étages...

Liste de pré-diviseurs HF. (non compatibles broche à broche.)

| Référence | Fmax | division |

| MB506 | 2,5 GHz | 256 |

| SP8704 | 1,0 GHz | 128 ou 64 |

| MC12058 | 1,1 GHz | 256 |

| SAB6456 | 1,1 GHz | 256 ou 64 |

| SA701D | 1,1 GHz | 129 |

| MC12026 | 1,1 GHz | 8 ou 16 |

Schéma de la partie BF.

La partie numérique abordée succinctement juqu'à là ne présente pas de grande difficulté; c'est même un bon point de départ pour s'initier au langage vhdl. La description à partir de ce langage permet de rendre le projet indépendant de toute cible (Xilinx, Altéra...). Le problème principal est bien sur les ressources nécessaire. Inévitablement, il faut diviser le 10 MHz pour obtenir une horloge de 1 seconde; par ailleurs, il faut le compteur du nombre d'impulsion du signal à mesurer pendant la seconde (autrement dit, la fréquence). La dimension de ce compteur caractérise la précision de la mesure. Inutile d'aller au-delà de la précision du TCXO, qui est de l'ordre du Hertz, ce qui fait un compteur de 30 bits pour un signal maximum de 1 GHz, 32 bits pour 2,5 GHz. Il sera interressant de regarder comment l'outil de synthèse permet l'implémentation d'un compteur... Pour des raisons exclusivement professionnelles, la cible utilisée ici est de la famille Xilinx ; les ressources nécessaires sont marginales, un FPGA d'entrée de gamme suffira parfaitement. (Spartan II XC2S15)

| Référence | XC2S50E | XC2S100E | XC2S150E | XC2S200E | XC2S300E |

| Nb de Slices | 768 | 1200 | 1728 | 2352 | 3072 |

| Nb de block RAM | 8-32kb | 10-40kb | 12-48kb | 14-56kb | 16-64kb |

| Mémoire IsP | XCF01S | XCF01S | XCF02S | XCF02S | XCF02S |

Caractéristiques commune aux différentes références :

Famille Spartan IIE, alimentation 1,8Volts.

Boîter PQ208, utilisation de 146 broches, 28x28mm.

Speed grades -6-7 permettant le fonctionnement des DLL jusqu'à 320 MHz et des bascules ??.

Optimisation des performences du montage :

La référence de temps utilisera un TCXO à 10 MHz et 10ppm de précision (soit 1 Hertz).

En dessous de 200 MHz, l'entrée LF est utilisée permettant la précision de mesure maximale, soit 1 Hertz.

Petite considération pratique et exemples.

Il faut trouver un compromis entre la précision et la rapidité de mesure. Ceci est directement induit par

la prédivision HF externe. Dans notre cas, cette pré division par 128 nécessite d'effectuer 7 décalages à gauche

avant affichage; on perd donc de l'information, pour améliorer la précision, on doit compter sur plusieurs

secondes.

prenons un exemple concret : une fréquence de 1 GHz, soit

7 812 500 Hz après division par 128,

111 0111 0011 0101 1001 0100 en binaire,

111011100110101100101000000000 après 7 décalages.

L'erreure de fréquence maximale correspond à l'écart avec des 1, soit :

111011100110101100101001111111

ce qui représente 1 000 000 127

On interprète donc que l'utilisation du rapport 64 pour le prédiviseur aménera à une erreure maximale de

63 Hertz. Si, avec ce rapport, le calcul est effectué sur une durée de 2 secondes, l'erreure sera de 31 Hertz...

Pour obtenir une précision de 1 Hertz il est donc nécessaire de compter une durée en seconde équivalente au

facteur de prédivision.

3. Codage & simulation de la partie numérique.

Le code VHDL est indépendant de la cible, bien sur. Cible qui s'est portée ici sur la famille xilinx (Altera aurait

très bien fait l'affaire, mais je ne connais pas du tout).

Pour une présentation des composants FPAGA Xilinx et les différentes familles, se reporter à l'introduction

FPGA & VHDL.

Le composant choisit est un SPARTAN IIE, car guère plus chère que le SPARTAN II et plus rapide. (technologie de

gravure plus fine).

Le boitier sera de type PQ208, le plus commun et dont on peu envisager la soudure, à la maison, tard le soir

après un bol de café.

Le nombre de porte sera de 100k à 200k, selon la disponibilité du composant. (XC2S100E ou XC2S200E).

La PROM associée permet de mémoriser le programme; soit une OTP XC17S100A (ou 200A) dans le cas d'une absolue

certitude du code source, plus stoïquement (courageusement) la PROM XCF02S sera très bien.

La encore, se reporter au document ci-dessus pour quelques mots sur les PROM.

Passons aux choses sérieuses, le code vhdl qui pilote tout cela.

La simulation est réalisée sous Simili (symphony EDA) logiciel libre dans sa version de base.

L'éditeur peut-être emacs, logiciel GNU, libre qui dispose de toutes les fonctions vhdl (coloration syntaxique ainsi

que quelques outils bien pratiques...)

Code vhdl et test bench au format html: frequencemètre.

La capture de la simulation présente les signaux lors de la mémorisation de la fréquence mesurée ; ici, pour des

raisons de temps de simulation, la fréquence est mesurée sur 1ms et non 1 seconde ! le fichier à implémenter

travaillera, quant à lui, avec le signal top_seconde.

On constate donc, le ballayage des afficheurs sel_0to9 valant 001/002/004/008/010/020/040/080/100/200. la valeur 7

ségments associée à chaque afficheur.

4. Réalisation pratique :

Le circuit sera réalisé sur une plaque époxy double face avec plan de masse. La partie relative aux afficheurs sept segments est reportée sur un plaque annexe (face avant).

Caractéristiques techniques. Gamme de fréquence : Voie 1 : DC à 250 MHz. Voie 2 : 250MHz à 2,5GHz. Sensibilité : Voie 1 : 20mVRMS à +-5V. (A MESURER) Voie 2 : 30mVRMS à +-3V. (IDEM)

5. Pour compléter :

A partir de là, plusieurs mesures complémentaires sont possibles, les temps de montée et de descente des signaux

par exemple. Il peut être par ailleurs interessant de disposer d'une éventuelle atténuation de 10 sur l'entrée

ainsi que du choix de l'impédance (50 Ohms ou 1MOhms). L'activation d'un filtre optionnel passe bas de 100kHz pour

les mesures en basse fréquance qui permettrait d'éviter les perturbations HF. Si une deuxième voie est réalisée,

fonctionnant simultannément, il est alors possible de mesurer les différences de fréquence ou de phase entre ces

deux voies... Une diode de statut renvoie l'état de fonctionnement en face avant ; si elle est éteinte, le signal

ne déclenche pas le compteur; si elle reste allumée, c'est que le signal est trop fort et qu'il y a saturation ;

quand elle clignote le signal est correctement acquis.

6. Documentation et bibliographie :

B. Wehkamp, Funkschau, Munich, N°9/86 p69.

Electronique pratique, N°249, Fréquencemètre 2 GHz.

Nouvelle électronique, N°20, Mars 1996 Fréquencemètre 2,3GHz.

Electronique Radio Plan, N°548, juillet 1993 Compteur universel HP-53131.

Note 1 : Heinrich Hertz (1857-1894) fut le premier à produire et à détecter des ondes électromagnétiques à une fréquence de l'ordre de 1GHz