Le moteur provient de l'universitť de berkeley : spice3f5.

Plusieurs interfaces existent autour de ce simulateur.

PSPICE est une version commercialisťe par Orcad/Cadence.

Protel permet aussi la simulation analogique ŗ partir du schťma.

Simulation aussi basťe sur le moteur spice. (netlist de l'ampli op issue de Protel/spice).

L'utilisation d'Opus Spice est prťsentťe ici.

Ce logiciel est libre de droit, sans restrictions apparentes et disponible sous Linux ou Zindow$.

Il est possible d'interfacer le simulateur avec le logiciel bien connu de CAO Eagle,

ici l'entrťe se fera par un script, la sortie en mode graphique.

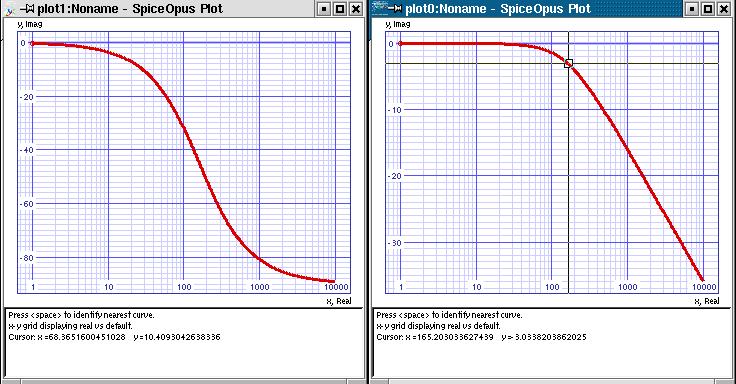

Exemple 1 : simulation de la fonction de transfert d'un filtre RC.

objectif : reprťsenter une fonction de transfert en gain & phase.

mots clefs : plot db, plot ph, ac dec

Filtre RC simple

.control

set units=degree

ac dec 50 1 10k

plot db(v(Vout))

plot ph(v(Vout))

.endc

* Filtre RC d'ordre 1

* Frťquence d coupure ŗ 3dB = 1/2*pi*R*C

* soit ici, pour R=10k et C=100n fc=162Hz

* pente de 20dB par dťcades

R1 N1 Vout 10K

C1 Vout 0 100N

Ve N1 0 0V

+AC 1 0 PULSE 0 -1 0 1US

* note : pulse ne sert pas ici

.end

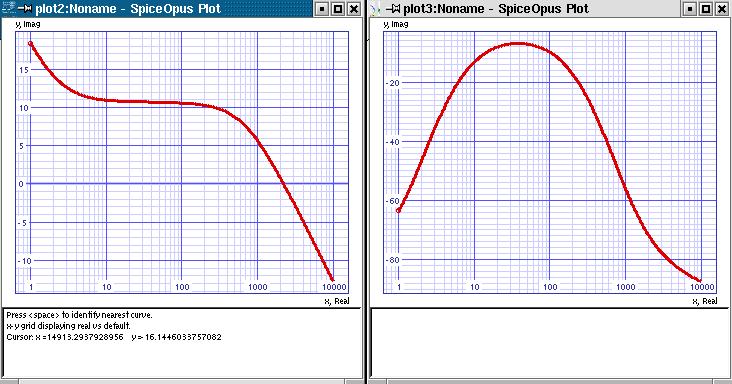

Rťsultat de simulation. frťquence de coupure ŗ 3dB de 162Hz, pente 20dB/dťcade (ordre 1)

Exemple 2 : fonction de transfert ŗ partir de la transformťe de Laplace.

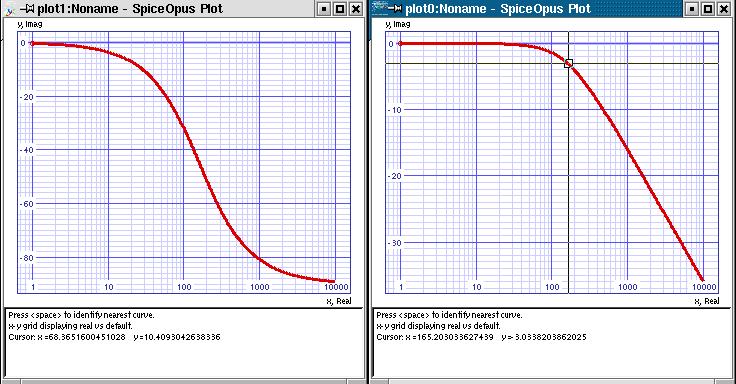

Exemple 3 : Amplificateur opťrationnel inverseur.

objectif : utiliser un composant dans la description, reprťsentation temporelle.

mots clefs : SUBCKT, include, model, tran

La fonction subckt est utilisťe pour dťfinir le composant amplificateur ua741.

Le modŤle utilisť ici est fournit ŗ la fin du document. (annexe 1)

Le rapport gain bande/passante est constant (faire plusieurs simulations).

La saturation peut aussi Ítre observťe avec une entrťe suffisemment importante.

Amplificateur inverseur

.control

set units=degree

ac dec 50 0.1 1000k

plot db(v(Vs))

plot ph(v(Vs))

tran 50us 200us 0 50us

plot v(N1) v(Vs)

.endc

* Amplificateur inverseur

* gain de -R2/R1

* ici, 20*log(100k/10k) = 20dB

* dťphasage de 180 degrŤs.

.SUBCKT ua741 VPLUS VMINUS VOUT VCC VEE

.INCLUDE ua741.cir

.MODEL BC107 NPN (BF=150 RB=100 VA=200 CCS=2PF CJE=3PF CJC=2PF TF=0.3NS TR=6NS)

.MODEL BC177 PNP (BF=80 RB=20 VA=200 CJE=6PF CJC=4PF TF=1NS TR=20NS)

.ends

R1 N1 Vm 10K

R2 Vm Vs 100K

Ve N1 0 0.5V

*+AC 1 0 PULSE 0 -1 0 30US

+AC 1 0 SIN 0.1 0.1 10k 0 0 0

VCC VCC 0 15V

VEE 0 VEE 15V

X1 0 Vm Vs VCC VEE ua741

.end

Rťsultat de simulation. Observation de la bande passante du modŤle pour un gain donnť.

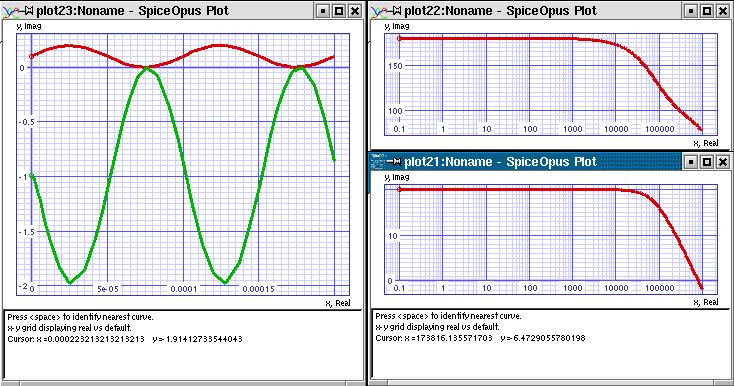

Exemple 4 : Filtre de boucel actif.

L'objectif cette fois est de visualiser les diagrammes de Bode.

On notera le pole et le zťro de la fonction de transfert.

Ils correspondent aux deux points d'inflexion de la courbe de gain.

respectivement 0.1Hz et 10Hz.

Filtre de boucle actif n/p

.control

set units=degree

ac dec 50 0.01 100

plot db(v(OUT))

plot ph(v(OUT))

*tran 50us 200us 0 50us

*plot v(N1) v(OUT)

.endc

* Amplificateur inverseur

* gain de -R2/R1

* ici, 20*log(100k/10k) = 20dB

* dťphasage de 180 degrŤs.

.SUBCKT LF411C 1 2 3 4 5

.INCLUDE LF411C.cir

.ends

C1 NetC1_1 Netrinb_2 100nF

C2 OUT NetC1_1 10uF

C3 0 NetC4_1 10uF

C4 NetC4_1 NetRina_2 100nF

R1 Netrinb_2 NetC1_1 159K

R3 NetRina_2 NetC4_1 159K

RINA INP NetRina_2 15.9K

RRINB INM Netrinb_2 15.9K

XU1 NetRina_2 Netrinb_2 VCC VEE OUT LF411C

VCC VCC 0 15V

VEE 0 VEE 15V

VIN INP INM 0

+AC 1 0 SIN 0 5 50k 0 0 0

.end

Rťsultat de simulation.

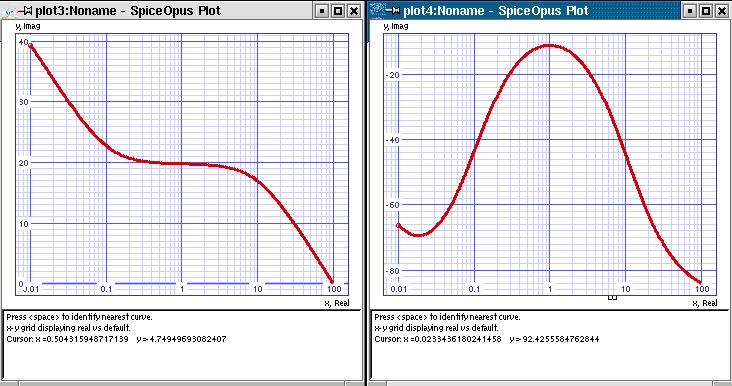

Exemple 5 : Filtre de boucel actif.

Exemple 5 : Filtre de boucel actif.

Le circuit est similaire au prťcťdent, il prťsente une cellule de prť-filtrage en T

sur chacune des entrťes diffťrentielles de l'amplificateur opťrationnel.

Filtre de boucle actif n/p avec prť-filtrage en T

.control

set units=degree

ac dec 50 1 10k

plot db(v(OUT))

plot ph(v(OUT))

.endc

.SUBCKT LF411C 1 2 3 4 5

.INCLUDE LF411C.cir

.ends

R2m NetC1_1 Vm 33k

C2m OUT NetC1_1 2.2uF

Rcr Vm OUT 1000K

R2p Vp NetC4_1 33K

C2p 0 NetC4_1 2.2uF

R1a INP N1p 4.7K

C1a N1p 0 100nF

R1b N1p Vp 4.7K

R1c INM N1m 4.7K

C1b N1m 0 100nF

R1d N1m Vm 4.7K

XU1 Vp Vm VCC VEE OUT LF411C

VCC VCC 0 15V

VEE 0 VEE 15V

VIN INP INM 0

+AC 1 0 SIN 0 1 1k 0 0 0

.end

Rťsultat de simulation.

Annexe 1 :

Exemple de modŤle pour ua741.

Peu performent, difficile d'utilisation.

*Autogenerated from schematic ua741.sch

*Do not edit anything except lines starting with '+'

*TP1 ? VEE B1,27

*TP2 ? VPLUS B1,27

*TP3 ? VMINUS B1,27

*TP4 ? VOUT B1,27

*TP5 ? VCC B1,27

C1 N21 N20 30P

Q16 N12 NI21 NI22 BC107

QI1 N1 VPLUS N4 BC107

QI2 N1 VMINUS N6 BC107

QI3 N2 N17 N4 BC177

QI4 N20 N17 N6 BC177

QI5 N2 NI12 NI13 BC107

QI6 N20 NI12 NI14 BC107

QI7 VCC N2 NI12 BC107

QI8 N1 N1 VCC BC177

QI9 N17 N1 VCC BC177

QI10 N17 NI16 NI15 BC107

QI11 NI16 NI16 VEE BC107

QI12 NI17 NI17 VCC BC177

QI13 N21 NI17 VCC BC177

QI14 N21 N16 N12 BC107

QI15 N12 N20 NI21 BC107

QI17 N20 N27 VEE BC107

QI18 N21 N26 VOUT BC107

QI19 N27 N24 VOUT BC177

QI20 N27 N27 VEE BC107

QI21 VCC N21 N26 BC107

QI22 VEE N12 N24 BC177

R1 VEE NI13 1K

R2 VEE NI12 50K

R3 VEE NI14 1K

R4 VEE NI15 5K

R5 VEE NI21 50K

R6 VEE NI22 100

R7 NI16 NI17 39K

R8 N16 N21 4.5K

R9 N12 N16 7.5K

R10 VOUT N26 50

R11 N24 VOUT 25

Annexe 2 :

Exemple de modŤle pour LF411C.

*.SUBCKT LF411C 1 2 3 4 5

C1 11 12 3.498E-12

C2 6 7 15E-12

DC 5 53 DX

DE 54 5 DX

DLP 90 91 DX

DLN 92 90 DX

DP 4 3 DX

BGND 99 0 V=V(3)*.5 + V(4)*.5

BB 7 99 I=I(VB)*28.29E6 - I(VC)*30E6 + I(VE)*30E6 + I(VLP)*30E6 - I(VLN)*30E6

GA 6 0 11 12 282.8E-6

GCM 0 6 10 99 1.59E-9

ISS 3 10 DC 195E-6

HLIM 90 0 VLIM 1K

J1 11 2 10 JX

J2 12 1 10 JX

R2 6 9 100E3

RD1 4 11 3.536E3

RD2 4 12 3.536E3

RO1 8 5 50

RO2 7 99 25

RP 3 4 15E3

RSS 10 99 1.026E6

VB 9 0 DC 0

VC 3 53 DC 2.2

VE 54 4 DC 2.2

VLIM 7 8 DC 0

VLP 91 0 DC 30

VLN 0 92 DC 30

.MODEL DX D(IS=800E-18)

.MODEL JX PJF(IS=12.5E-12 BETA=250.1E-6 VTO=-1)

*.ENDS LF411C