- A chacun des niveaux plesiochrones (2 - 8 - 34 - 140 Mbit/s) est ajouté un en-tête POH (Path Over Head); il regroupe les informations de service, la justification (gigues et dérapages) et la mesure de qualité de bout en bout.

- A 150 Mbit/s, en plus du POH, un en-tête SOH (Section Over Head) est ajouté. Il permet la synchronisation et le contrôle de la qualité de chaque système de ligne ; il véhicule par ailleurs des voies de services.

1. Structure de la trame SDH.

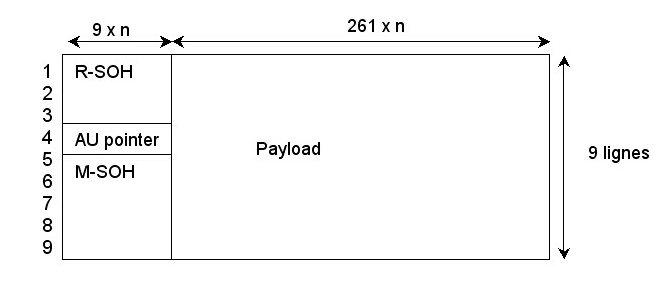

Le signal de la hiérarchie SDH est organisé en trame de 125 us, période d'échantillonnage du signal téléphonique. Il est ainsi possible d'insérer un canal téléphonique, d'une capacité de 64 kbit/s à des endroits spécifiques de la trame. Une trame STM-1 est représentée sous la forme d'une matrice d'octet de 9 lignes par 270 colonnes ; le nombre de trame étant de 8000 par seconde, le débit nominal est de 155 520 kbit/s. Les 9 premiers octets de chaque ligne constituent le SOH, en-tête de section qui permet, entre autre, de synchroniser la trame, puis par la suite de repérer les diverses informations utiles. Cette trame de base peut ensuite être multiplier par n afin d'obtenir un débit supérieur STM-n. Format de la trame STM-1. La première ligne du SOH permet le verrouillage de la trame sur la séquence 3.n.A1 plus 3.n.A2 avec

A1=xF6 et A2=x28 ; l'octet J0 est un octet du message de trace de la section de régénération. A l'exception des 9.n octets de la première ligne du SOH, la trame est embrouillée par l'intermédiaire du polynôme 1 + x6 + x7 et ce afin de s'affranchir de la présence du mot de verrouillage de trame dans la charge. Voir G707 pour plus de détails.

La première ligne du SOH permet le verrouillage de la trame sur la séquence 3.n.A1 plus 3.n.A2 avec

A1=xF6 et A2=x28 ; l'octet J0 est un octet du message de trace de la section de régénération. A l'exception des 9.n octets de la première ligne du SOH, la trame est embrouillée par l'intermédiaire du polynôme 1 + x6 + x7 et ce afin de s'affranchir de la présence du mot de verrouillage de trame dans la charge. Voir G707 pour plus de détails.

2. Multiplexage synchrone.

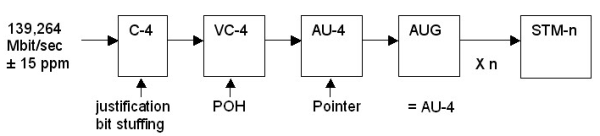

Un conteneur virtuel, ou VC, est une structure construite à partir d'un signal de type plésiochrone auquel nous avons ajoutés un en-tête appelé POH. Chaque VC est accessible individuellement et de façon indépendante à l'intérieur de la trame STM-n, et ce par l'intermédiaire de l'information de pointeurs. Affluent E4 dans un signal STM-1. L'affluent PDH E4 est mappé dans un conteneur C-4 incluant un mécanisme de justification au niveau

bit afin de pouvoir absorber les plus ou moins 15 ppm du 139 264 kBit/s. Le C-4 est de taille fixe

de 260*9=2340 octets auquel nous ajoutons un en-tête POH afin d'obtenir un conteneur virtuel d'ordre 4 ou VC-4. Le VC-4 est flottant à l'intérieure du STM-n, la valeur du pointeur d'AU-4 véhiculée par les octets H2 et H3 permet de repérer l'origine du conteneur dans la charge : le pointeur indique la position de l'octet J1 du POH. La valeur de pointeur associée au VC-4 constituent un AU-4 ou Unité Administrative d'ordre 4.

Caractéristiques des neufs octets du POH (niveau VC-3 ou VC-4).

L'affluent PDH E4 est mappé dans un conteneur C-4 incluant un mécanisme de justification au niveau

bit afin de pouvoir absorber les plus ou moins 15 ppm du 139 264 kBit/s. Le C-4 est de taille fixe

de 260*9=2340 octets auquel nous ajoutons un en-tête POH afin d'obtenir un conteneur virtuel d'ordre 4 ou VC-4. Le VC-4 est flottant à l'intérieure du STM-n, la valeur du pointeur d'AU-4 véhiculée par les octets H2 et H3 permet de repérer l'origine du conteneur dans la charge : le pointeur indique la position de l'octet J1 du POH. La valeur de pointeur associée au VC-4 constituent un AU-4 ou Unité Administrative d'ordre 4.

Caractéristiques des neufs octets du POH (niveau VC-3 ou VC-4).

| J1 | J1 | Path trace |

| B3 | B3 | Bip8 parity control |

| C2 | C2 | Signal label (mapping) |

| G1 | G1 | Path status |

| F2 | F2 | Path user channel |

| H4 | H4 | Position and sequence indicator |

| F3 | F3 | Path user channel |

| K3 | Z3 | Automatic Protection Switch |

| N1 | Z4 | Tandem Connection Monitoring |

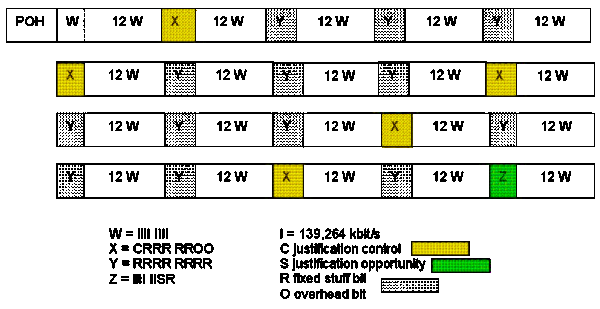

- 1934 bits d'information : bits I

- 1 bit d'opportunité de justification : bit S

- 5 bits de controle de justification : bits C

- 13*8+5*7+1=140 bits de bourrage (stuff) : bit R

Chaque ligne dispose de 1934 bits d'informations et 1 bit d'opportunité de justification. L'affluents plésiochrone que l'on peut mapper peut présenter des dérives de fréquence dans la limite de plus ou moins 15 ppm. Le bit de justification permet alors d'absorber les variations par rapport au débit nominal.

Chaque ligne dispose de 1934 bits d'informations et 1 bit d'opportunité de justification. L'affluents plésiochrone que l'on peut mapper peut présenter des dérives de fréquence dans la limite de plus ou moins 15 ppm. Le bit de justification permet alors d'absorber les variations par rapport au débit nominal.

3. AU-3 ou TU-3.

Un mécanisme identique au précédent permet d'insérer trois débits à 34 368 Mbit/s dans la trame SDH. Dans ce cas, le débit PDH est mappé dans un conteneur synchrone C-3. L'adjonction du POH permet de créer un VC-3 ; la gestion des pointeurs d'AU génère un AU-3. Il est alors possible d'insérer trois AU-3 dans une trame SDH STM-1, chacune d'entre elle est repérée par un triplet H1/H2/H3 contenu dans le SOH. Une autre possibilité consiste à passer par un TU-3; dans ce cas, le l'affluent E3 ou DS3 est mappé pour constituer un C-3. L'ajout du POH permet de générer un VC-3 qui est ensuite organisé en TU-3 et non plus en AU-3 comme avant. 3 TUG-3 (de 86 colonnes chacun) sont entrelacés au niveau octet à l'intérieur de la charge du VC-4.

<--------------- TUG-3 = 86 Colonnes --------------->

1 2 3 4 5 6 7 8 9 ... 86

+------------------------------------------------------+

1 |H1| |

|H2| |

|H3| |

9 rangées |S | |

|t | _________________________________|

|u |_________________|J1 |

|f | B3 |

|f | C2 |

9 | | G1 ...Charge C-3... |

+------------------------------------------------------+

<---------------- VC-4 = 260 Colonnes ------------------------>

1 2 3 4 5 6 7 8 9 ... 261

+---------------------------------------------------------------+

1 |J1| | |

|B3| | |

|C2|S S| |

9 rangées |G1|t t| T T T T T |

|F2|u u| U U U U U |

|H4|f f| G G G G G |

|F3|f f| 3 3 3 3 3 |

|K3| | # # # # # |

9 |N1|1 2| 1 2 3 1 2 ... |

+---------------------------------------------------------------+

Le TUG-3 fut défini afin de limiter le nombre trop important de possibilité d'insertion d'un VC d'ordre faible à l'intérieur d'un VC d'ordre plus élevé. Les TUG contiennent donc différent groupes de TU qui sont entrelacés au niveau octet et positionnés à des endroits fixes, donc sans pointeur.

La gestion des pointeurs est ainsi simplifiée, elle consiste à repérer la charge VC-4 au lieu de 3 charges VC-3, ya trois fois moins de boulot, vois tu, OH OH compagnons, la rumeur qui gronde au sein des masses... Cette remarque est d'autant plus valable que le débit est faible; un signal 2048 sera donc mappé dans un VC-12, gérer au niveau des pointeurs dans un TU-12 entrelacés dans un VC-3 soit 7 TU-12 dans un VC-3.

Différentes structures de multiplexage possibles.

| Type de conteneur VC | Largeur de bande du VC-i | Charge utile du C-i |

|---|---|---|

| VC-11 | 1 664 kbit.s | 1 600 kbit.s |

| VC-12 | 2 240 kbit.s | 2 176 kbit.s |

| VC-2 | 6 848 kbit.s | 6 784 kbit.s |

| VC-3 | 48 960 kbit.s | 48 384 kbit.s |

| VC-4 | 150 336 kbit.s | 149 760 kbit.s |

| VC4-4c | 601 344 kbit.s | 599 040 kbit.s |

| VC4-16c | 2 405 376 kbit.s | 2 396 160 kbit.s |

| VC4-64c | 9 621 504 kbit.s | 9 584 640 kbit.s |

| VC4-256c | 38 486 016 kbit.s | 38 338 560 kbit.s |

- justif=00 alors ajout de 8 + 7 bits soit un bloc de 1431 bits et un débit total de 3*8000*1431 = 34 344 kbit/s

- justif=01 alors ajout de 8 + 8 bits soit un bloc de 1431 bits et un débit total de 3*8000*1432 = 34 368 kbit/s

- justif=11 alors ajout de 8 + 9 bits soit un bloc de 1431 bits et un débit total de 3*8000*1433 = 34 392 kbit/s

4. Pointeur d'AU-4 & pointeur d'AU-3.

L'objectif du pointeur d'AU-n est multiple :- Indiquer la position de l'octet J1 dans la charge STM-n.

- Compenser les offsets de fréquences des éléments de réseaux.

| AU-4 pointer | AU-3 pointer | ||||

|---|---|---|---|---|---|

| H1 | Y | Y | H1 | H1 | H1 |

| H2 | 1 | 1 | H2 | H2 | H2 |

| H3 | H3 | H3 | H3 | H3 | H3 |

1 : all one

- Chacun des doublets H1/H2 pointe sur l'octet J1 du VC-i associé.

- H1 et H2 représentent la valeur du pointeur.

- La valeur du pointeur est un nombre compris entre 0 & 782.

- C'est le nombre de position possible dans la charge : 782 = (270*9 - 9*9)/3.

- Ce nombre indique le nombre d'octet entre le dernier H3 et le J1 du VC-i.

- C'est une valeur qui est donnée par incrément de 3 octets.

- H3 est une valeur d'opportunité de justification dont nous allons détailler l'usage.

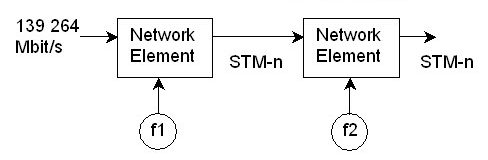

L'horloge de traitement f1 du premier équipement génère le VC-4 inséré dans la trame STM-n ; tous les mécanismes sont synchrones de la même horloge f1, il n'set donc pas nécessaire d'adapter le VC-4 à la trame STM-n de sortie. Par contre le deuxième équipement fonctionnera à une fréquence f2 alors que le VC-4 sera synchrone de f1 ; le STM-n de sortie sera généré synchrone de f2, il en résulte qu'il faut adapter les écarts de fréquences par l'opportunité de justification H3 qui sera associé à une incrémentation ou décrémentation de valeur de pointeur. Les ajustements de pointeurs doivent être séparés par au moins trois trames à l'intérieure desquelles la valeur reste constante : au maximum une justification toutes les 4 trames. Et donc au maximum 2000 justifications par seconde ; le mouvement de pointeur AU-4 bougera la charge VC-4 de 3 octets (3 H3) soit 24 bits ce qui représente une variation de plus ou moins 48 kbit/s autour du débit nominal de 155520*361/270 = 150 360 kbit/s soit un écart de fréquence de + ou - 319 ppm.

L'horloge de traitement f1 du premier équipement génère le VC-4 inséré dans la trame STM-n ; tous les mécanismes sont synchrones de la même horloge f1, il n'set donc pas nécessaire d'adapter le VC-4 à la trame STM-n de sortie. Par contre le deuxième équipement fonctionnera à une fréquence f2 alors que le VC-4 sera synchrone de f1 ; le STM-n de sortie sera généré synchrone de f2, il en résulte qu'il faut adapter les écarts de fréquences par l'opportunité de justification H3 qui sera associé à une incrémentation ou décrémentation de valeur de pointeur. Les ajustements de pointeurs doivent être séparés par au moins trois trames à l'intérieure desquelles la valeur reste constante : au maximum une justification toutes les 4 trames. Et donc au maximum 2000 justifications par seconde ; le mouvement de pointeur AU-4 bougera la charge VC-4 de 3 octets (3 H3) soit 24 bits ce qui représente une variation de plus ou moins 48 kbit/s autour du débit nominal de 155520*361/270 = 150 360 kbit/s soit un écart de fréquence de + ou - 319 ppm.

5. Modification et interprétation du pointeur.

Le codage du pointeur d'AU est situé dans les octets H1&H2 dont les bits 1 à 16 sont "NNNNSSID | IDIDIDID" avec :- I : bit d'augmentation.

- D : bit de diminution.

- N : bit NDF fanion de données nouvelles.

- SS : type de charge.

L'information NDF est activée lorsqu'au moins 3 des 4 bits N correspondent à "1001".

L'information NDF est désactivée lorsqu'au moins 3 des 4 bits N correspondent à "0110".

Les bits transportant l'information NDF permettent un changement arbitraire de la valeur du pointeur. Exemple de modification de valeur de pointeur :

| Frame | NNNNSS | IDIDIDIDID | H1H2 |

| ----- | 0110SS | 0101101101 | 365 |

| i | 0110SS | 0101101101 | 365 |

| i+1 | 0110SS | 1111000111 | inc |

| i+2 | 0110SS | 0101101110 | 366 |

| j | 0110SS | 0101101101 | 365 |

| j+1 | 0110SS | 0000111000 | dec |

| j+2 | 0110SS | 0101101100 | 364 |

Le champs H1/H2 pouvant être une valeur de pointeur ou une information de justification, il est nécessaire d'opérer un séquencement. En fonctionnement normal, le champs indique la localisation du début du conteneur VC-n ds la trame d'AU-n. Une valeur doit être reçue trois fois de suite, puis suivie d'une opération de justification. (calcul sur les bits I & D) En cas de décalage de fréquence entre le débit de trame du groupe AUG et celui du conteneur VC-n, la valeur du pointeur sera augmentée ou diminuée & accompagnée d'un ou plusieurs octets correspondant de justification positive ou négative. Des opérations de pointeur doivent être séparés par au moins trois trames. (donc peuvent se présenter toutes les 4 trames.) Si le débit du conteneur VC-n est trop rapide par rapport à celui du groupe d'AUG, l'alignement du conteneur VC-n doit être périodiquement avancé, et la valeur du pointeur diminuée d'une unité. Cette opération est effectuée en inversant les bits D (8-10-12-14-16) du mot de pointeur. Cette introduction terminée, nous pouvons aborder l'insertion d'un affluent 2048 kbit/s dans la trame SDH puis regarder les cas particuliers de concaténation contigüe. Ethernet over SDH : GFP.

Lexique.

plésiochrone : le débit est presque le même (à 10-6 près)

pour toutes les artères de même type.

PDH : Plesiochonous Digital Hierarchy

SDH/NHS : Synchronous Digital Hierarchy/Hiérarchie Numérique Synchrone

SONET : Synchronous Optical Network

POH : Path Over Head

SOH : Section Over Head

RSOH : En tête de Section de Régénération

MSOH : En tête de Section de Multiplexage

STM-n : Synchronous Transport Module level n

STS-n : Synchronous Transport Signal level n

SPE : Synchronous Payload Envelope

VC : Virtual Container (POH+payload)

VT : Virtual Tributary

AU : Administrative Unit

AUG : Administrative Unit Group

TU : Tributary Unit

TUG : Tributary Unit Group

NDF : New Data Flag